# FPGA Implementation of BIKE for Quantum-Resistant TLS

Andrea Galimberti, Davide Galli, Gabriele Montanaro, William Fornaciari and Davide Zoni

EasyChair preprints are intended for rapid dissemination of research results and are integrated with the rest of EasyChair.

August 30, 2022

# FPGA implementation of BIKE for quantum-resistant TLS

Andrea Galimberti DEIB Politecnico di Milano Milano, Italy andrea.galimberti@polimi.it Davide Galli DEIB Politecnico di Milano Milano, Italy davide11.galli@mail.polimi.it Gabriele Montanaro DEIB Politecnico di Milano Milano, Italy gabriele.montanaro@polimi.it William Fornaciari DEIB Politecnico di Milano Milano, Italy william.fornaciari@polimi.it

Davide Zoni DEIB Politecnico di Milano Milano, Italy davide.zoni@polimi.it

Abstract-The recent advances in quantum computers impose the adoption of post-quantum cryptosystems into secure communication protocols. This work proposes two FPGA-based, client- and server-side hardware architectures to support the integration of the BIKE post-quantum KEM within TLS. Thanks to the parametric hardware design, the paper explores the best option between hardware and software implementations, given a set of available hardware resources and a realistic use-case scenario. The experimental evaluation comparing our client and server designs against the reference AVX2 and hardware implementations of BIKE highlighted two aspects. First, the proposed client and server architectures outperform the reference hardware implementation of BIKE by eight and four times, respectively. Second, the performance comparison between our client and server designs against the reference AVX2 implementation strongly depends on the available resource. Our solution is almost twice as fast as the AVX2 implementation while implemented on the Artix-7 200 FPGA, while it is up to six times slower when targeting smaller FPGAs, thus motivating a careful analysis of the available hardware resources and the optimization of the design's parallelism before opting for hardware support.

Index Terms—Post-quantum cryptography, code-based cryptography, QC-MDPC codes, hardware accelerators, BIKE, FPGA

#### I. INTRODUCTION

Public-key cryptography (PKC) [1]–[3] allows exchanging keys over an insecure channel without sharing a secret key. Its technology is at the core of current secure communication protocols such as Transport Layer Security (TLS) [4] and Secure Shell (SSH) [5]. TLS is the most widely used cryptographic protocol, providing encryption to the HTTPS communication protocol, secure communication in mobile apps, and encrypted access to email servers.

Notably, the security of current public-key cryptography relies on the hardness of factoring large integers and of computing discrete logarithms in a cyclic group. However,

algorithms such as Shor's [6] can solve these problems in polynomial time on quantum computers, whose recent technological advances threaten to break traditional PKC and, consequently, the secure communication protocols that make use of it [7]. To mitigate such risk, post-quantum cryptography (PQC) aims to develop cryptosystems that are secure against attacks from quantum and classical computers and can interoperate with existing communications protocols and networks [8]. In this scenario, the US National Institute of Standards and Technology (NIST) is currently leading a standardization process to identify a set of post-quantum algorithms to replace current public-key cryptosystems. Submitted proposals span over a wide portion of state of the art in computational theory, including algebraic geometry [9], coding theory [10], and lattice theory [11]. Despite the theoretical differences, each proposal must satisfy two requirements. First, post-quantum cryptosystems must leverage computationally hard problems that even quantum computers cannot solve in polynomial time. Second, their computational complexity and the importance of their adoption in scenarios ranging from HPC to resourceconstrained platforms force NIST to also require efficient hardware implementations in addition to traditional software ones. Specifically, the NIST PQC standardization process selected the Intel Haswell CPUs and Xilinx Artix-7 FPGAs as the software and hardware targets.

From the theoretical point of view, code-based cryptography has a remarkably good security track, dating back to the McEliece cryptosystem [10] proposed in 1978, thus motivating its adoption by several candidates of the NIST PQC standardization process. However, the strong security and performance of the original McEliece cryptosystem, which employs binary Goppa codes [12], come at the cost of large memory requirements, in the order of megabits, to store the key pairs. To this end, quasi-cyclic moderate-density parity-check (QC-MDPC) codes [13] emerged as an effective alternative to binary Goppa codes, reducing the key size of code-based cryptosystems to

This work was supported by the EU Horizon 2020 "TEXTAROSSA" project (Grant No. 956831).

tens of kilobits while maintaining security against quantum attacks. BIKE [14] is a key encapsulation mechanism (KEM) based on QC-MDPC codes, and it is a current candidate for standardization in the fourth round of the NIST PQC initiative [15].

Despite the vast literature targeting efficient hardware support for BIKE, each proposal is meant to deliver novel computing platforms aiming either to maximize the performance or to minimize the resource utilization of the hardware, without *i*) considering the integration of the hardware support in current secure communication protocols, such as TLS, and *ii*) addressing the critical question of the actual advantage of employing hardware support in place of an optimized software implementation. Indeed, state-of-the-art lacks a complete comparison to identify the best implementation strategy between hardware and software, considering the available computational resources.

**Contributions** - This paper presents a complete hardware implementation of BIKE that targets the Xilinx Artix-7 family of FPGAs and supports client and server KEM operations in a quantum-resistant TLS [16]. The proposed architecture leverages a set of state-of-the-art configurable accelerators [17]–[19] that implement the key operations of the KEM primitives to provide the best hardware support. Our architecture is evaluated against the reference AVX2 software [20] and FPGA-based hardware [21] implementations of BIKE.

Apart from the complete hardware implementation of BIKE, the novelty of this work concerns the analysis between different hardware and software state-of-the-art implementations of BIKE. The goal is to highlight the best option between hardware and software implementations, given a set of available hardware resources and a realistic use-case scenario. This is in contrast to previous state-of-the-art, which usually targets the design of efficient hardware support without considering i) the application of a complete KEM scheme and ii) a comparison between optimized hardware and software implementations. More in detail, the two main contributions of our work are listed below.

- Efficient hardware support for BIKE in TLS The proposed solution delivers two architectures tailored to the client and server operations of a quantum-resistant TLS integrating the BIKE KEM. The parametric components, taken from the state of the art, are integrated into a complete design of the KEM primitives. The experimental results show that the proposed client and server designs outperform the reference hardware implementation of BIKE [21] by 9 and 6 times, respectively.

- Design space exploration and guidelines A design space exploration based on our complexity-based heuristic allows selecting the parameters of the components integrated into the proposed client and server architectures to provide the best hardware support given the available resources. The extensive comparison between the reference AVX2 implementation and our designs demonstrates the performance advantage of the hardware

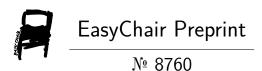

Fig. 1: KEM operations in post-quantum TLS handshake [16].

implementation, with a speedup up to  $1.91\times$ , if the available hardware resources are, at least, those of Artix-7 35 and 200 FPGAs for the TLS server and client use cases, respectively. Otherwise, the software implementation overcomes the hardware one by up to 6 times.

The rest of the paper is organized into four parts. Section II discusses the background of BIKE and TLS and the state-of-the-art targeting hardware realizations for QC-MDPC codebased cryptosystems. Section III presents the client- and server-side architectures to support BIKE operations in TLS, as well as the complexity-based heuristic used in our design space exploration. Section IV discusses the experimental results, while some design guidelines and conclusions are drawn in Section V.

#### II. BACKGROUND AND RELATED WORKS

This section discusses the background of BIKE and TLS as well as the state of the art for QC-MDPC code-based cryptosystems. The background discussion emphasizes identifying the computational complexity within the BIKE KEM when employed within TLS. In contrast, the state-of-the-art analysis focuses on the hardware implementations for QC-MPDC codes that can be applied to BIKE.

# A. Background

**Quantum-resistant TLS** - In TLS 1.3, the handshake phase between the client and server nodes is required to establish a shared secret key, useful to generate session keys which are then employed within a symmetric cryptosystem to efficiently exchange encrypted data [4]. The establishment of such shared secret requires making use of public-key cryptography. Diffie-Hellman [2] currently represents the most commonly employed public-key cryptosystem in TLS 1.3. However, the goal of designing a quantum-resistant TLS imposes instead the use of a post-quantum KEM such as the ones currently part of the NIST PQC standardization process [16]. Figure 1 shows the three main steps of the handshake phase between clients and servers when employing a post-quantum KEM in a post-quantum version of TLS [16].

First, the client performs the key generation primitive, producing a private-public key pair and sending the public key to the server. The server node then generates a shared secret and encrypts it with the public key of the client. Finally, the client retrieves the shared secret by decapsulating with its own private key the ciphertext received by the server node. As a result, the client and server endpoints obtained the same shared secret.

TLS 1.3 mandates using ephemeral keys to enforce the perfect forward secrecy (PFS) property. The design of a computationally efficient key generation primitive is thus as crucial as the encapsulation and decapsulation ones.

BIKE key encapsulation mechanism - BIKE [14] is a QC-MDPC code-based KEM, based on the Niederreiter cryptosystem, that leverages quasi-cyclic matrices with coefficients over  $\mathbb{Z}_2$ . The employed quasi-cyclic matrices are composed of  $n_0$  circulant blocks with size  $p \times p$ , that can be equivalently represented by  $n_0$  binary polynomials in  $GF(2^p)$ , with coefficients equal to the first row of the corresponding circulant blocks. The arithmetic of  $p \times p$  circulant matrices over  $\mathbb{Z}_2$  is equivalent to the arithmetic of binary polynomials in  $\mathbb{Z}_2[x]/(x^p+1)$ . The addition of two binary polynomials in  $\mathbb{Z}_2[x]/(x^p+1)$  corresponds to their bit-wise XOR, while their multiplication consists in their carry-less multiplication followed by a modular reduction with respect to the  $x^p + 1$ irreducible polynomial. Moderate-density parity-check codes feature sparse parity-check H matrices, i.e., only a small percentage of values are set to 1, allowing for a sparse representation by enumerating the positions of bits set to 1. QC-MDPC codes possess both the quasi-cyclic and moderatedensity properties.

In the rest of this section, we describe the key generation, encapsulation, and decapsulation primitives of the BIKE key encapsulation mechanism by making use of the following notation.

$e = [e_0|e_1]$  is a random *n*-bit error vector with  $t \approx \sqrt{n}$ bits set to 1, where n = 2p and each  $e_i$  is a *p*-bit vector.  $H = [h_0|h_1]$  is the private key, composed of two circulant blocks  $h_i$  of size  $p \times p$ , with  $v \approx \sqrt{n}$  bits set to 1 for each row of each block  $h_i$ . *h* is the public key, which is a circulant block of size  $p \times p$ . *s* is the syndrome. *m* is a message. *c* is the ciphertext. *K* is the shared secret.

| Algorithm 1 | Key | generation | primitive | of BIKE [14]. |

|-------------|-----|------------|-----------|---------------|

|-------------|-----|------------|-----------|---------------|

| 1: <b>f</b> | function $[H,\sigma,h]$ KeyGen ( ) |

|-------------|------------------------------------|

| 2:          | seed = TRNG ();                    |

| 3:          | H = PRNG(SHAKE256(seed));          |

- 4:  $h_{0_{inv}} = \text{Invert}(h_0);$

- 5:  $h = h_1 \odot h_{0_{inv}};$

6:  $\sigma = \text{TRNG}();$

7: **return**  $\{H, \sigma, h\};$

Key generation - Algorithm 1 details the key generation primitive, that requires the pseudorandom generation of the public key  $H = [h_0|h_1]$  (line 3), the binary polynomial inversion (line 4) of  $h_0$ , and the binary polynomial multiplication (line 5) between the sparse  $h_1$ , with Hamming weight equal to v, and the dense  $h_{0_{inv}}$ . The key generation primitive outputs the private key H, the corresponding public key h, and a 256-bit message  $\sigma$ .

| Algorithm 2 | Encapsulation | primitive | of BIKE [14]. |

|-------------|---------------|-----------|---------------|

|-------------|---------------|-----------|---------------|

| 1: <b>f</b> u | unction $[K, c]$ ENCAPS $(h)$                                           |

|---------------|-------------------------------------------------------------------------|

| 2:            | m = TRNG ();                                                            |

| 3:            | e = PRNG(SHAKE256(m));                                                  |

| 4:            | $s = e_0 \oplus (e_1 \odot h);$                                         |

| 5:            | $m' = m \oplus \operatorname{Trunc}_{256}(\operatorname{SHA3-384}(e));$ |

| 6:            | $c = \{s, m'\};$                                                        |

| 7:            | $K = \text{Trunc}_{256}(\text{SHA3-384}(\{m, c\}));$                    |

| 8:            | return $\{K, c\};$                                                      |

*Encapsulation* - Algorithm 2 details the encapsulation primitive, which takes as its only input the public key h. Such primitive consists in the execution of the pseudorandom bits generation function, which employs SHAKE256 (see line 3) to generate the n-bit error vector e with Hamming weight equal to t, of a binary polynomial multiplication (see line 5) between the sparse  $e_1$ , with Hamming weight up to t, and the dense h, and two hashing operations making use of the SHA3-384 cryptographic hash function, respectively of n-bit (line 5) and (p + 512)-bit (line 7) messages. The concatenation of the syndrome s and the message m' obtained at lines 4 and 6, respectively, corresponds to the ciphertext c, that can then be sent from the server node to the client endpoint within the handshake phase, while the 256-bit digest K obtained at line 7 is the shared secret.

| Alg | <b>gorithm 3</b> Decapsulation primitive of BIKE [14].                     |

|-----|----------------------------------------------------------------------------|

| 1:  | <b>function</b> $[K]$ DECAPS $(H, \sigma, c)$                              |

| 2:  | $s' = h_0 \odot s;$                                                        |

| 3:  | e' = Decode(s', H);                                                        |

| 4:  | $m'' = m' \oplus \operatorname{Trunc}_{256}(\operatorname{SHA3-384}(e'));$ |

| 5:  | $a = (e' = \text{PRNG}(\text{SHAKE256}(m''))) ? m'' : \sigma;$             |

| 6:  | $K = \text{Trunc}_{256}(\text{SHA3-384}(\{a, c\}));$                       |

| 7:  | return K;                                                                  |

Decapsulation - Algorithm 3 lists the key operations that compose the decapsulation KEM primitive, which takes as its inputs the H public key, the ciphertext c, and the  $\sigma$  message. They are one binary polynomial multiplication (line 2 of Algorithm 3), where the  $h_0$  operand is sparse with Hamming weight equal to v, one instance of QC-MDPC bit-flipping decoding (line 3), the computations of two 384-bit hash digests through SHA3-384, respectively of n-bit (line 4) and (p+512)bit (line 6) messages, and the pseudorandom generation (line 5) of a polynomial with Hamming weight equal to t. The decapsulation primitive outputs the shared secret K.

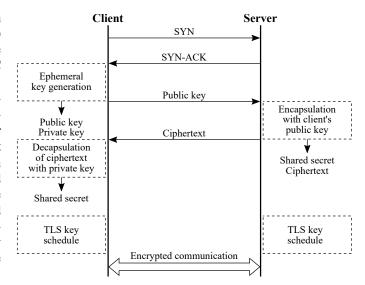

Fig. 2: Top-view architecture of the key generation module. Dashed blocks are shared with the Decaps module (see Figure 3).

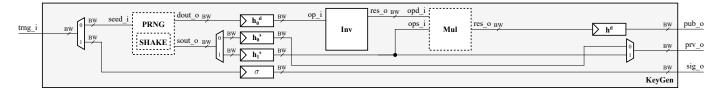

Fig. 3: Top-view architecture of the decapsulation module. Dashed blocks are shared with the KeyGen module (see Figure 2).

## B. State of the art

The literature contains several proposals targeting efficient hardware implementations for QC-MDPC code-based cryptosystems. [22], [23] proposed the implementation of the McEliece cryptosystem with QC-MDPC codes on FPGAs. In particular, [22] targeted a performance-oriented design while [23] focused on a resource-optimized one. [24] discussed a fast implementation of QC-MDPC Niederreiter encryption for FPGAs, outperforming the work in [22] thanks to using a hardware module to estimate the Hamming weight of large vectors and proposing a hardware implementation tailored to low-area devices for encryption and decryption used in QC-MDPC code-based cryptosystems. [21] presented an FPGAbased implementation of BIKE, which provided support for the key generation, encryption, and decryption KEM primitives, but it is custom-tailored to small FPGA targets.

Several other works focused instead on the optimal design of single key operations to support QC-MDPC code-based cryptosystems. [25] considered the FPGA-based design of two polynomial multipliers for BIKE, one implementing the multiplication between two dense operands and one implementing the multiplications between a dense and a sparse operand. [18] proposed a binary polynomial multiplier for dense-sparse multiplications that can be configured to scale across a variety of FPGA targets. [26] discusses a Karatsuba multiplier for dense binary polynomials, whose performance is, however, insufficient compared to a multiplier tailored to dense-sparse multiplication, when one of the two operands has a low Hamming weight. [19] presented a bit-flipping decoder for generic QC-MDPC codes that is highly configurable in terms of bandwidth and degree of parallelism, allowing it to scale across a range of FPGA targets. [27] also proposed a bitflipping decoder for QC-MDPC codes, that is, however, only configurable in the bandwidth of its datapath. [17] described a configurable architecture for binary polynomial inversion that scales across the entire Artix-7 FPGA family and makes use of the Karatsuba binary polynomial multiplier proposed in [26].

## III. METHODOLOGY

This section presents the scalable architectures of BIKE to support client and server KEM operations in TLS and the complexity-oriented heuristic for design space exploration. The scalability of the client and server architectures is obtained by mixing state-of-the-art configurable components for the most complex operations with hard-coded ones. The client and server architectures employ configurable components to implement binary polynomial inversion [17], binary polynomial multiplication [18], and OC-MDPC bit-flipping decoding [19]. The decoding component was adapted to implement the Black-Gray-Flip (BGF) decoding algorithm employed by BIKE and introduced in [28]. Fixed, non-parametric components [29] implement instead the SHA3-384 and SHAKE256 operations. Considering the pseudorandom generation functionality, we wrapped up the SHAKE256 component, as described in [21], to produce random bitvectors with the desired Hamming weight. The proposed design space exploration heuristic leverages the time- and space-complexity analysis of the employed configurable components to steer the fast identification of the combination of parameters that delivers the best hardware support.

The rest of this section is organized into three parts. Section III-A and Section III-B present the client and the server architectures, respectively, while the complexity-oriented heuristic is discussed in Section III-C.

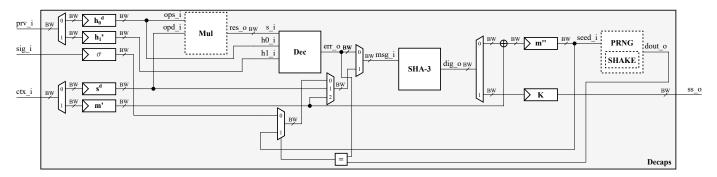

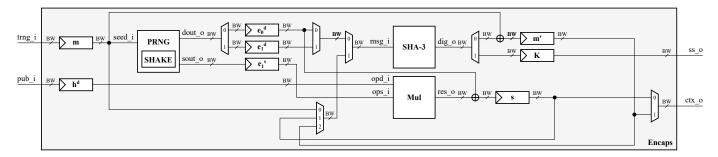

Fig. 4: Top-view architecture of the encapsulation module.

#### A. Client architecture

The client architecture implements the cryptographic core to support the client-side execution of BIKE in TLS. The architecture of the client consists of two main modules, key generation (KeyGen) and decapsulation (Decaps), which are depicted in Figure 2 and Figure 3, respectively. To minimize duplicate hardware resources, the pseudorandom generator (PRNG) and the multiplier (Mul) are shared between the modules (see dashed blocks in Figure 2 and Figure 3).

Key generation module - The KeyGen module, depicted in Figure 2, implements Algorithm 1. It features a BWbit input (trng\_i) to receive a 256-bit random value from the external true random number generator (TRNG), and outputs the public (h) and private (H) keys using the pub\_o and prv\_o outputs, respectively. Notably, the random output value  $\sigma$  that is part of the key generation procedure (see Algorithm 1), is produced by the external TRNG during the key generation procedure and output via the sig\_o port.

The implementation of the key generation algorithm of BIKE requires performing three subsequent hardware operations, namely pseudorandom generation (PRNG), binary polynomial inversion (Inv), and binary polynomial multiplication (Mul). The PRNG component is tasked with generating the private key H, producing the  $h_0$  polynomial in both the sparse and dense forms, and the sparse-only form for  $h_1$ . The dense-represented  $h_0$  polynomial is then inverted by the Inv component, whose output is finally multiplied by the sparse  $h_1$  within the Mul component. Mul produces the public key h, that is output through the pub\_o BW-bit port, while the private key H is output through the prv\_o BW-bit port.

**Decapsulation module** - The Decaps module, shown in Figure 3, implements Algorithm 3. It features three BW-bit inputs to receive the private key  $H(prv_i)$ ,  $\sigma(sig_i)$ , and the shared secret encrypted by the server  $c(ctx_i)$ , and it outputs the shared secret K through ss\_0.

The implementation of the decapsulation primitive of BIKE requires performing a sequence of four hardware operations, namely binary polynomial multiplication (Mul), QC-MDPC bit-flipping decoding (Dec), computation of SHA-3 hash digest (SHA-3), and pseudorandom generation (PRNG). The dense syndrome s, which is part of the ciphertext c, is multiplied by the sparse polynomial  $h_0$ , obtaining the s' vector, which is then fed to the Dec module together with H to decode it and obtain the e' *n*-bit vector. The latter is hashed by the SHA-3 module and the resulting digest is XORed with m', obtaining m''. If the result of the pseudorandom generation seeded by m'' is equal to e', then the SHA-3 module computes the digest of  $\{m'', c\}$ , i.e., m'' concatenated to the ciphertext c, otherwise it hashes  $\{\sigma, c\}$  to avoid information leakage while also raising a decapsulation error flag. In case of a successful decoding, the resulting digest is the shared secret, which is output by the ss\_0 BW-bit port.

#### B. Server architecture

The server architecture implements the cryptographic core to support the server-side execution of BIKE in TLS. The architecture of the server consists of the encapsulation module (Encaps). Although the software execution of the encapsulation is significantly faster than the more complex key generation and decapsulation, the web server scenario foresees a multitude of concurrently active TLS connections, thus mandating for efficient hardware support also for encapsulation.

**Encapsulation module** - The Encaps module, which is depicted in Figure 4, implements Algorithm 2. It takes as inputs a 256-bit random message m and the public key h through the BW-bit trng\_i and pub\_i ports, respectively, and outputs the shared secret K, through ss\_i, and the ciphertext c, i.e., the shared secret encrypted with the public key received from the client, through ctx\_0.

The implementation of the encapsulation primitive of BIKE requires performing a sequence of three hardware operations, namely pseudorandom generation (PRNG), binary polynomial multiplication (Mul), and computation of the SHA-3 hash function (SHA-3). m is first expanded by the PRNG component to generate the random error vector  $e = [e_0|e_1]$ with Hamming weight t, and the dense-represented h is then multiplied by the sparse-represented  $e_1$  in the Mul component. The resulting product is then XORed with  $e_0$ , obtaining the syndrome s. m' is computed by XORing the message m with the SHA-3 hash digest of the error vector e, and the concatenation of s and m' corresponds to the ciphertext c. Finally, the shared secret K is produced as the SHA-3 hash digest of the message m concatenated to the ciphertext c. cis output through the ctx\_o BW-bit port, while the ss\_o BW-bit port outputs the shared secret K.

|                |         | TLS      | TLS server |         |               |         |  |

|----------------|---------|----------|------------|---------|---------------|---------|--|

| Operation      | Key gei | neration | Decaps     | ulation | Encapsulation |         |  |

|                | AES-128 | AES-192  | AES-128    | AES-192 | AES-128       | AES-192 |  |

| PRNG           | 7%      | 5%       | 2%         | 1%      | 29%           | 33%     |  |

| Invert         | 90%     | 94%      | -          | -       | -             | -       |  |

| Multiply       | 3%      | 1%       | 1%         | 1%      | 21%           | 26%     |  |

| SHA3-384       | -       | -        | 3%         | 2%      | 50%           | 41%     |  |

| Decode         | -       | -        | 93%        | 95%     | -             | -       |  |

| Execution time | 0.21    | 0.69     | 0.83       | 2.69    | 0.05          | 0.11    |  |

TABLE I: Breakdown of relative execution time for each operation, expressed as a percentage, and total execution time, expressed in milliseconds, of AVX2 software KEM primitives.

#### C. Design space exploration

In order to provide the best hardware support, the proposed client and server architectures leverage a set of state-of-the-art configurable accelerators for the most complex operations employed within the KEM primitives. However, such flexibility comes at the cost of a broad design space, which imposes the use of an efficient search strategy to minimize the exploration time.

Therefore, a four-step complexity-oriented heuristic drives the design space exploration according to the time and space complexity of the most computationally intensive operations in the three KEM primitives. We note that the overall computation time on the client side can be considered as the sum of the execution times of the key generation and decapsulation KEM primitives [14], while encapsulation represents the sole serverside functionality. Moreover, the configurable components employed to implement multiplication [18], inversion [17], and decoding [19] highlight block RAM (BRAM) as the scarcest resource thus their space complexity can be approximated as the sum of BRAMs used for key generation and decapsulation, on the client side, and for encapsulation, on the server side.

In the following, we describe the four steps of the employed heuristic.

**Step 1** - Starting from the computational time of the AVX2 implementation of BIKE, the heuristic computes the fraction of time spent executing each primitive in the server and the client. Table I shows that the fraction of time for key generation and decapsulation is 20% and 80%, respectively, on the client side, while the encapsulation represents the entire server time. Such ratios are used to assign the amount of resources devoted to each KEM primitive module in the client and server architectures.

**Step 2** - For each KEM primitive module, the heuristic identifies the operations executed by parametric components that require the largest fraction of execution time. In particular, the heuristic considers the set of parametric operations for which the execution time is at least 90% of the total execution time of the primitive or the entire set of configurable components otherwise. Table I shows that multiplication is the sole parametric operation in our implementation and accounts for up to 26% of the encapsulation time. In contrast, decoding, which is computed by a configurable component, accounts for more than 90% of the execution time in the AVX2 implementation of decapsulation. **Step 3** - For each component or group of components, the heuristic explores time- and space-complexity formulas to identify the combination of parameters that allows maximizing performance within the assigned resource budget. The exhaustive search in the parameter space to find out the best parameter configurations for each module is very fast since it leverages the configurable components' time- and space-complexity formulas without involving any time-consuming hardware synthesis and place-and-route tasks.

Step 4 - The heuristic implements the client and server designs employing the configurations obtained at Step 3. Notably, our algorithm is robust and conservative to account for *i*) the nonpredictability of the synthesis and implementation of EDA tools, and *ii*) the fact that a small change in the parameters can severely affect the performance and resource utilization. Therefore, the heuristic could land to an unfeasible configuration or to a configuration for which not all the available resources can be used since small increments in the parameters would make it unfeasible within the resource budget. In the former case, the heuristic iteratively re-implements the failed design by lowering the values of the parameters for which the time-complexity formulas show the smallest performance degradation, and this process keeps on until the design becomes feasible. In the latter case, the heuristic iteratively reimplements the non-optimal design by increasing the values of the parameters for which the space-complexity formulas highlight the smallest resource utilization increase, until either the performance improvement is lower than a certain threshold or the design saturates the available hardware resources.

TABLE II: Parameters of QC-MDPC codes for BIKE [14].

| Code | Security | p     | t   | v   | iter |

|------|----------|-------|-----|-----|------|

| B1   | AES-128  | 12323 | 134 | 71  | 5    |

| B3   | AES-192  | 24659 | 199 | 103 | 5    |

#### IV. EXPERIMENTAL EVALUATION

This section analyzes the area and performance of the instances of the proposed quantum-resistant TLS client and server architectures identified through the design space exploration. The rest of this section is organized in two parts. Section IV-A provides an overview of the BIKE code parameters and of the experimental setup, while Section IV-B details the area and performance results.

TABLE III: Area results for the proposed and reference [21] client cores, expressed in terms of look-up tables (LUT), flipflops (FF), and block RAM (BRAM), and relative resource utilization, expressed as a percentage within round brackets.

|           | Our        |       |       |             |        | BIKE [21] |                  |       |       |                 |        |       |

|-----------|------------|-------|-------|-------------|--------|-----------|------------------|-------|-------|-----------------|--------|-------|

| Code      | Artix-7 50 |       |       | Artix-7 200 |        |           | Lightweight (LW) |       |       | High-speed (HS) |        |       |

|           | LUT        | FF    | BRAM  | LUT         | FF     | BRAM      | LUT              | FF    | BRAM  | LUT             | FF     | BRAM  |

| B1        | 31792      | 17805 | 43.5  | 126510      | 51492  | 357       | 11454            | 4602  | 14    | 43084           | 610    | 39    |

| DI        | (98%)      | (27%) | (58%) | (94%)       | (19%)  | (98%)     | (55%)            | (11%) | (28%) | (32%)           | (2%)   | (11%) |

| B3        | 31411      | 20181 | 45.5  | 124891      | 53067  | 360       |                  |       | _     |                 |        |       |

| D5        | (96%)      | (31%) | (61%) | (93%)       | (20%)  | (99%)     | -                | -     | -     | -               | -      | -     |

| Available | 32600      | 65200 | 75    | 134600      | 269200 | 365       | 20800            | 41600 | 50    | 134600          | 269200 | 365   |

TABLE IV: Area results for the proposed and reference [21] server cores, expressed in terms of look-up tables (LUT), flipflops (FF), and block RAM (BRAM), and relative resource utilization, expressed as a percentage within round brackets.

| Our        |                                         |                                                                |                                                                                                    |                                                                                                                                | BIKE [21]                                                                                                                                                             |                                                          |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|-----------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Artix-7 35 |                                         |                                                                | Artix-7 200                                                                                        |                                                                                                                                |                                                                                                                                                                       | Lightweight (LW)                                         |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | High-speed (HS)                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LUT        | FF                                      | BRAM                                                           | LUT                                                                                                | FF                                                                                                                             | BRAM                                                                                                                                                                  | LUT                                                      | FF                                                                                                                                                                                                                        | BRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LUT                                                                                                                                                                                                                                                                 | FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BRAM                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19804      | 11401                                   | 30                                                             | 91422                                                                                              | 46208                                                                                                                          | 275.5                                                                                                                                                                 | 6730                                                     | 3298                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14829                                                                                                                                                                                                                                                               | 3471                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (95%)      | (27%)                                   | (60%)                                                          | (68%)                                                                                              | (17%)                                                                                                                          | (75%)                                                                                                                                                                 | (32%)                                                    | (8%)                                                                                                                                                                                                                      | (6%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (6%)                                                                                                                                                                                                                                                                | (1%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (3%)                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19979      | 12282                                   | 28                                                             | 72725                                                                                              | 37795                                                                                                                          | 235.5                                                                                                                                                                 |                                                          |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (96%)      | (30%)                                   | (56%)                                                          | (54%)                                                                                              | (14%)                                                                                                                          | (65%)                                                                                                                                                                 | -                                                        | -                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                |